| Visual C++ 2010 Express ソースコード(spd_chk.cpp) |

- #include "stdafx.h"

- #include "cusb2.h"

- #include "spa3.h"

-

-

- //#define DEBUG_SPA3

- //#define WAIT_DISP

-

- #ifdef DEBUG_SPA3

- u8 spa3_bit[1024*64];

- #else

- u8 spa3_bit[]=

- #include "spa3_bit.inc"

- #endif

|

6行目のDEBUG_SPA3を有効にすると、ISEが生成したbitファイルを直接読み込んでFPGAのコンフィグを行います。

7行目のWAIT_DISPを有効にすると、ブロックRAMを使用して収集した待ち時間を表示します。 |

- #define MODE_IDLE 0

- #define MODE_START 1

-

- #define DIR_FX2PC 0 //EP6IN (FX2 -> PC) transfer

- #define DIR_PC2FX 1 //EP2OUT(PC -> FX2) transfer

-

- #define BUF_LEN 1024*64

- #define QUE_NUM 16

|

1−2行目はPCアプリからFPGAに転送中/停止中を伝えるための定義です。

4-5行目はPCアプリからFPGAに転送方向を伝えるための定義です。

7−8行目は同期転送用のスレッドを起動する際に、指定する転送バッファの長さと個数です。 |

- #define START_SEED32 0x12345678

-

- class cusb2 *usb;

- class spa3 *spa3;

-

- cusb2_tcb *tcb1;

-

- s32 max_cnt;

- s32 cnt;

- s32 err_cnt;

|

| 6行目は同期転送用のスレッドを制御するためのタスクコントロールブロックへのポインタです。 |

- #define PORT_BITS 35 //PC<->FPGA間のポートビット数(入力と出力は同じビット数)

-

- struct{//出力(PC -> FPGA)ポート

- u64 init_val :32;

- u64 DIR : 1;

- u64 MODE : 1;

- u64 RST : 1;

- } out_port;

-

- struct{//入力(FPGA -> PC)ポート

- u64 wait_cnt :31;

- u64 cmp_err : 1;

- } in_port;

|

JTAG ポートの定義です。

出力ポートでFPGAの動作モード、設定などを行い。

入力ポートでFPGA状態を取得します。

1行目は大きいほうの出力ポート35bitになっています。 |

- bool fx2pc_func(u8 *buf, u32 len){

- static u32 cnt32=START_SEED32;

- u32 i,*p;

- p = (u32 *)buf;

- for(i=0; i < (len/4); i++)

- {

- if(p[i] != cnt32++)

- {

- if(err_cnt < 5)

- printf("\nerr in %8.8X %8.8X != %8.8X\n", cnt*BUF_LEN+i*4,

p[i], cnt32-1);

- err_cnt++;

- }

- }

- if(cnt++ < max_cnt) return true;

-

- spa3->ep6in_stop();

-

- out_port.MODE = MODE_IDLE;

- spa3->port(PORT_BITS, (u8 *)&out_port, (u8 *)&in_port);

- return false;

- }

|

同期転送スレッドから呼び出されるコールバック関数です。FX2 -> PCにデータが届いた際に呼び出されます。

ポインタbufにデータのポインタ、lenにデータの長さがセットされて呼ばれます。この例では単純にファイルに書きためています。コールバック関数は戻り値が重要で、引き続きデータを受信(送信)しつづける際にはtrueを返し、送受信を終了する際にはfalseを返すようにします。

16行目はSPA3ライブラリのep6in_stop()関数を呼び出し、FX2に対して転送を停止するように指示しています。

18-19行目はJTAGポート機能を使用して、FPGAに対して転送モードの終了を指示しています。 |

- bool pc2fx_func(u8 *buf, u32 len){

- static u32 cnt32=START_SEED32;

- u32 i,*p;

- p = (u32 *)buf;

- for(i=0; i < (len/4); i++)

- {

- p[i] = cnt32++;

- }

- if(cnt++ < max_cnt+QUE_NUM) return true;

-

- spa3->ep2out_stop();

-

- out_port.MODE = MODE_IDLE;

- spa3->port(PORT_BITS, (u8 *)&out_port, (u8 *)&in_port);

- return false;

- }

|

同期転送スレッドから呼び出されるコールバック関数です。PC -> FX2に転送するデータを作成するために、バッファに空きが出来た際に呼び出されます。

事前に送信用のデータをキューの数だけ作成することになります。ですのでこの関数が呼ばれる回数は、実際に送信したキューの数+作成したキューの数になる点にご注意ください。

他の処理は上のコールバック関数と同様です。 |

- void wait_and_showinfo(){

- usb->delete_thread(tcb1);

- if(err_cnt != 0)

- {

- printf(" NG(err=%d).\n", err_cnt);

- }

- else

- {

- printf(" OK.\n");

- }

- //printf("%fMbps\n",48.0*16.0* (BUF_LEN*max_cnt/2)/(BUF_LEN*max_cnt/2+(in_port.wait_cnt

& 0x7fffffff))); //48MHz 16bit

- printf("%fMbps\n",30.0*16.0* (BUF_LEN*max_cnt/2)/(BUF_LEN*max_cnt/2+(in_port.wait_cnt

& 0x7fffffff))); //30MHz 16bit

- if(in_port.cmp_err)

- printf("FX2 compare err!!\n");

- }

|

転送速度を表示する関数です。

2行目で同期転送スレッドを削除しています。

11−12行目はIFCLKの周波数、待ち時間などから実際の転送速度を計算しています。 |

- void disp_wait(u16 *buf){

- s32 i;

- u32 max = 0;

- u32 max2 = 0;

- u32 ave = 0;

-

- for(i = 0; i < 1024; i++){

- printf("%4.4X ", buf[i]);

- if(i%8 == 7) printf("\n");

- if(buf[i] > max){

- max2 = max; //最大値は起動前に待たされた分になるので、2番目を使用

- max = buf[i];

- }

- ave += buf[i];

- }

- printf("wait cycle(48MHz) ave = %d max = %d.\n", ave/1024,

max2);

}

|

| ブロックRAMを使用して収集した待ち時間(Cycle)を表示する関数 |

- int _tmain(int argc, _TCHAR* argv[])

- {

- u64 dev_dna;

- #ifdef WAIT_DISP

- u16 wait16[1024];

- #endif

-

- #ifdef DEBUG_SPA3

- FILE *fp_spa3;

- fopen_s(&fp_spa3, "spa3a\\spd_chk.bit","rb");

- fread(spa3_bit, 1, sizeof(spa3_bit), fp_spa3);

- fclose(fp_spa3);

- #endif

-

- usb = new cusb2();

- spa3 = new class spa3();

- u8 t = 0;

- if(argc == 2)

- {

- char *s;

- t = (u8)strtol(argv[1], &s, 10);

- }

- dev_dna = 0;

- if(spa3->init(usb, &dev_dna, spa3_bit)) //Spartan3Aコンフィグレーション

- {

- printf("Device DNA = %8.8X%8.8X\n", (u32)(dev_dna >>

32), (u32)dev_dna);

|

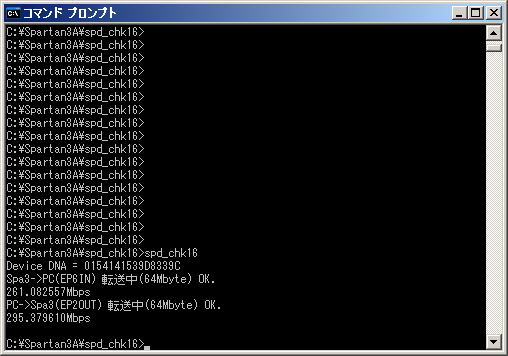

メイン関数です。

15-16行目でカメレオンUSB、SPA3クラスを実体化させています。

23行目でdev_dnaにゼロを指定することで、最初に見つけたカメSPA3を対象にします。

24行目でFX2にSPA3ファームウエアのロード、FPGAのコンフィグを行います。 |

- spa3->set_fifo_16(); //FIFO 16bit

- //spa3->ifconfig(0xE3); //slave FIFO, IFCLK=48MHz, IFCLK出力, 同期(Sync)モード

- spa3->ifconfig(0xA3); //slave FIFO, IFCLK=30MHz, IFCLK出力,

同期(Sync)モード

-

- out_port.init_val = START_SEED32;

- out_port.DIR = 0;

- out_port.MODE = MODE_IDLE;

- out_port.RST = 1;

- spa3->port(PORT_BITS, (u8 *)&out_port, (u8 *)&in_port);

-

- //SPA3Aリセット(初期パラメータロード)

- out_port.RST = 0;

- spa3->port(PORT_BITS, (u8 *)&out_port, (u8 *)&in_port);

|

1行目はFIFOを16bitに設定しています。

3行目はFX2のifconfigレジスタを設定することで、IFCLK 30MHzに設定します。(詳細はFX2のユーザマニュアルを参照)

5−9行目でFPGAに初期値の設定を行います。

11-13でFPGAのリセット(RST)を 1 -> 0にセットしています。 |

- cnt=err_cnt=0;

- max_cnt=1024;

- tcb1 = usb->start_thread(0x86, BUF_LEN, QUE_NUM, fx2pc_func);

-

- spa3->ep6in_start();

-

- out_port.DIR = DIR_FX2PC;

- out_port.MODE = MODE_START;

- spa3->port(PORT_BITS, (u8 *)&out_port, (u8 *)&in_port);

-

- printf("Spa3->PC(EP6IN) 転送中(%dMbyte)",BUF_LEN*max_cnt/(1024*1024));

- wait_and_showinfo();

|

3行目でFX2->PCへの同期転送スレッドを開始させます。0x86はエンドポイントEP6INのアドレスです。バッファ長、キューの数、コールバック関数を指定します。

5行目でFX2にEP6INの転送開始を指示します。

7−9行目でFPGAに対して、転送方向、転送開始を指示します。

12行目で転送終了を待ち、結果を表示します。 |

- #ifdef WAIT_DISP

- spa3->mem_read(0, 1024, wait16);

- disp_wait(wait16);

- memset(wait16, 0, sizeof(wait16));

- spa3->mem_write(0, 1024, wait16);

- #endif

|

JTAG RAMアクセス関数を使用して、FPGA内部のブロックRAMを読み出します。

読み出した後は、次の転送に備えて、初期化の書き込みを行います。 |

- out_port.RST = 1;

- spa3->port(PORT_BITS, (u8 *)&out_port, (u8 *)&in_port);

-

- //SPA3Aリセット(初期パラメータロード)

- out_port.RST = 0;

- spa3->port(PORT_BITS, (u8 *)&out_port, (u8 *)&in_port);

-

- cnt=err_cnt=0;

- max_cnt=1024;

- tcb1 = usb->start_thread(0x02, BUF_LEN, QUE_NUM, pc2fx_func);

-

- spa3->ep2out_start();

-

- out_port.DIR = DIR_PC2FX;

- out_port.MODE = MODE_START;

- spa3->port(PORT_BITS, (u8 *)&out_port, (u8 *)&in_port);

- printf("PC->Spa3(EP2OUT) 転送中(%dMbyte)",BUF_LEN*max_cnt/(1024*1024));

- wait_and_showinfo();

- #ifdef WAIT_DISP

- spa3->mem_read(0, 1024, wait16);

- disp_wait(wait16);

- #endif

- }

- delete usb;

- return 0;

- }

|

1-6行目でRSTを 1 -> 0にして、FPGAのリセットを行います。

10行目はPC->FX2への同期転送スレッドを開始させます。0x02はEP2OUTのアドレスです。バッファ長、キューの数、コールバック関数を指定します。

残りの処理はFX2->PCとほぼ同じです。 |